# INTERRUPT SERVICE SUBROUTINE

This work is licensed under the Creative Commons Attribution-NonCommercial-Share Alike 2.5 India License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-sa/2.5/in/deed.en or send a letter to Creative Commons, 171 Second Street, Suite 300, San Francisco, California, 94105, USA.

## INTERRUPT SERVICE SUBROUTINE

#### OBJECTIVE

To write an assembly language program to interrupt the 8085 microprocessor and to execute the interrupt service subroutine.

#### **APPARARTUS REQUIRED**

• Single board Microcomputer.

- Power supply.

- Flat Ribbon Cable.

- Bread board

- Resistors

- LED's.

- Wires.

### DESCRIPTION

An Interrupt Service Subroutine (ISS) is similar to a procedure that it may be branched from any other program and return branch is made to that program and return branch after interrupt routine has executed.

The interrupt routine must be written so that except for lapse in time the interrupted program proceeds first as if nothing had happened. This means that PSW and registers used by routine must be saved and restored and return must be made to instruction and that which follows last instruction executed before the interrupt.

## ALGORITHM

1.Intialize the stack pointer to store PSW.

2. Intialize 8255 in I/O made with all its port as output ports.

3. Using SIM and EI instructions RESET RST7.5 and mask if available.

4. Main program is obituary and here it is counting 00 to FF in an infinite loop.

5. Processor states are stored in PC.

6.Suitable delay program is made use or.

7.When interrupted by RST7.5 vector interrupt routine is executed. The PSW is disabled until interrupt routine is completed.

8.Interrupt is enabled and PSW is restored back.

## **CONNECTION DETAILS**

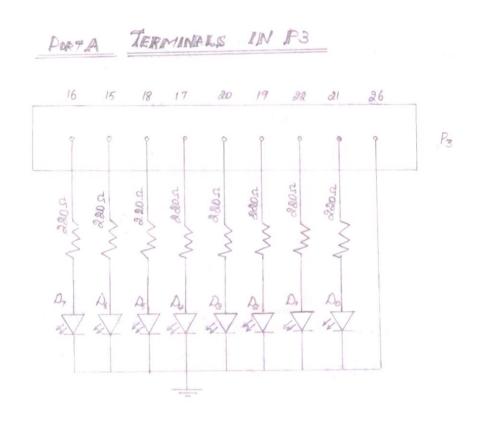

## **CONNECTION OF FRC TO LED**

| DATA                 | <b>D</b> <sub>7</sub> | $D_6$ | $D_5$ | $D_4$ | $D_3$ | $D_2$ | $D_1$ | $\mathbf{D}_{0}$ |

|----------------------|-----------------------|-------|-------|-------|-------|-------|-------|------------------|

| BITS                 |                       |       |       |       |       |       |       |                  |

| PIN NO               | 16                    | 15    | 18    | 17    | 20    | 19    | 22    | 21               |

| 26 <sup>TH</sup> PIN | - GR                  | OUNI  | D     |       |       |       |       |                  |

## SET INTERRUPT MASKS INSTRUCTION

| D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| SOD            | SDE            | х              | R7.5           | MSE            | M7.5           | M6.5           | M5.5           |

| Serial         | Serial         | Ignored        | Reset          | Mask           | RST7.5         | RST 6.5        | RST 5.5        |

| O/P            | Data           |                | RST7.5         | Set            | Mask           | Mask           | Mask           |

| Data           | Enable         |                | Flip           | Enable         |                |                |                |

| Ignored        | 0-disable      |                | flop           | 0-bits 0       |                |                |                |

| If $D_6=0$     | 1-enable       |                | 0-not          | to 2           |                |                |                |

|                |                |                | reset          | Ignored        |                |                |                |

|                |                |                | 1-             | 1-mask         |                |                |                |

|                |                |                | reset          | is set         |                |                |                |

| ADDRESS | LABEL | MNEMONICS                | OPCODE/OPERAND |

|---------|-------|--------------------------|----------------|

| C100    |       | LXI SP,C500 <sub>H</sub> | 31 00 C5       |

| C103    |       | MVI A,80 <sub>H</sub>    | 3E 80          |

| C105    |       | OUT CWR                  | D3 DB          |

| C107    |       | MVI A,1B <sub>H</sub>    | 3E 1B          |

| C109    |       | SIM                      | 30             |

| C10A    |       | EI                       | FB             |

| C10B    |       | MVI A,00 <sub>H</sub>    | 3E 00          |

| C10D    | DISP  | OUT PORTA                | D3 D8          |

| C10F    |       | MOV D,A                  | 57             |

| C110    |       | CALL DELAY               | CD 18 C1       |

| C113    |       | MOV A,D                  | 7A             |

| C114    |       | INR A                    | 3C             |

| C115    |       | JMP DISP                 | C3 0D C1       |

|         |       |                          | ·              |

| C118    | DELAY | LXI B, FFFF <sub>H</sub> | 01 FF FF       |

| C11B    | AGAIN | DCX B                    | 0B             |

| C11C    |       | MOV A,C                  | 79             |

| C11D    |       | ORA B                    | B0             |

| C11E    |       | JNZ AGAIN                | C2 1B C1       |

| C121    |       | RET                      | C9             |

|         |       |                          |                |

| C122    | ISS   | PUSH PSW                 | F5             |

| C123    |       | DI                       | F3             |

| C124    |       | MVI E,06H                | 1E 06          |

| C126    |       | XRA A                    | AF             |

| C127    | NEXT  | CMA                      | 2F             |

| C128    |       | OUT PORTA                | D3 D8          |

| C12A    |       | MOV M,A                  | 77             |

| C12B    |       | CALL DELAY               | CD 18 C1       |

| C12E    |       | MOV A,M                  | 7E             |

| C12F    |       | DCR E                    | 1D             |

| C130    |       | JNZ NEXT                 | C2 27 C1       |

| C133    |       | EI                       | FB             |

| C134    |       | POP PSW                  | F1             |

| C135    |       | RET                      | C9             |

## **PROGRAM TRACE**

| LABEL | MNEMONICS                   | DESCRIPTION                                                       |  |  |  |  |

|-------|-----------------------------|-------------------------------------------------------------------|--|--|--|--|

|       | LXI<br>SP,C500 <sub>H</sub> | Initialize the stack pointer.                                     |  |  |  |  |

|       |                             | C4FD XX<br>C4FE XX<br>C4FF XX<br>C500 XX STACK POINTER<br>C501 XX |  |  |  |  |

| <b>MVI</b> A,80 <sub>H</sub> | Initiali:<br>writing f                                                                                                                                                                                                                                                                                                                                                       | -                                                                                                                                                       | -                    |                     |                  |                            | 255 as        | O/P po               | orts by            |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|------------------|----------------------------|---------------|----------------------|--------------------|

|                              | witcilly                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                         | CIUI                 | wor                 | u as 00          |                            |               |                      |                    |

|                              | DATA                                                                                                                                                                                                                                                                                                                                                                         | D7                                                                                                                                                      | D <sub>6</sub>       | -                   | D <sub>4</sub>   | D <sub>3</sub>             | $D_2$         | $D_1$                | D <sub>0</sub>     |

|                              | BITS                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                       | 0                    | 0                   | 0                | 0                          | 0             | 0                    | 0                  |

|                              | COMMENT                                                                                                                                                                                                                                                                                                                                                                      | I/0                                                                                                                                                     | Mod                  |                     | PortA            | PortC                      | Mode0         | PortB                | PortC              |

|                              |                                                                                                                                                                                                                                                                                                                                                                              | mode                                                                                                                                                    |                      |                     | 0/P              | Upper<br>O/P               |               | O/P                  | Lower<br>O/P       |

| OUT CWR                      | Α 8<br>Β 2<br>D 2                                                                                                                                                                                                                                                                                                                                                            | SISTERS           30         XX           XX         XX           XX         XX           XX         XX           XX         XX           XX         XX | F<br>C<br>E<br>L     |                     |                  | 0 funct                    | ion for       | each ]               | port of            |

| MVI A,1B <sub>H</sub>        | $1B_{\rm H}$ is lo                                                                                                                                                                                                                                                                                                                                                           | aded in                                                                                                                                                 | n to                 | Acc                 | umulato          | r.                         |               |                      |                    |

|                              | A 1<br>B 2<br>D 2                                                                                                                                                                                                                                                                                                                                                            | SISTERS           B         XX           XX         XX           XX         XX           XX         XX           XX         XX           XX         XX  | F<br>C<br>L          |                     |                  |                            |               |                      |                    |

|                              | The execution of the SIM instruction uses the<br>contents of the accumulator (which must be previous)<br>loaded) to perform the following function<br><ul> <li>Program interrupt mask for the RST 5.5,RS<br/>6.5,RST 7.5 hardware interrupts.</li> <li>Reset the edge triggered RST 7.5 input latch.</li> <li>Load the SOD output latch.</li> </ul> <li>SIM INSTRUCTION</li> |                                                                                                                                                         |                      |                     |                  |                            | 5.5,RST       |                      |                    |

|                              | 000                                                                                                                                                                                                                                                                                                                                                                          | 008                                                                                                                                                     | v                    |                     | D7 E             | MOR                        | M7 E          | NC F                 | ME E               |

|                              | SOD<br>Serial                                                                                                                                                                                                                                                                                                                                                                | SDE<br>Serial                                                                                                                                           | <b>X</b><br>Unc      | lof                 | R7.5<br>Reset    | MSE<br>Mask                | M7.5<br>RST7. | <b>M6.5</b><br>5 RST | <b>M5.5</b><br>RST |

|                              | O/P                                                                                                                                                                                                                                                                                                                                                                          | Data                                                                                                                                                    | -ir                  |                     | RST7.5           | Set                        | Mask          | 5 RS1<br>6.5         | 5.5                |

|                              | Data                                                                                                                                                                                                                                                                                                                                                                         | Enable                                                                                                                                                  |                      |                     | Flip             | Enable                     |               | Mask                 |                    |

|                              |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                         |                      |                     | Flop             |                            |               |                      |                    |

|                              | When SOD                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                         |                      |                     |                  |                            | out fr        | om SOD.              |                    |

|                              | SIM INST                                                                                                                                                                                                                                                                                                                                                                     | Multip                                                                                                                                                  | urpo<br>mple<br>5,5. | se i<br>ment<br>5). | nstruct<br>the   | ion.                       | inte          | errupts              | (RST               |

|                              | •                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                         | ~~~                  |                     | - <u>-</u> ~ • • |                            |               |                      |                    |

|                              | •<br>                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                         |                      |                     |                  |                            |               |                      |                    |

|                              | •                                                                                                                                                                                                                                                                                                                                                                            | NSTRUCT                                                                                                                                                 |                      |                     |                  | RIPTION                    |               |                      |                    |

|                              |                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                         |                      | BIT<br>1            |                  | <b>RIPTION</b><br>5.5 is n | narked (      | or disal             | pled.              |

|      |                  |                                                                                                 | -                                                                                                                 | 1                 |                                       |

|------|------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------|

|      |                  | D <sub>1</sub>                                                                                  | M6.5                                                                                                              | 1                 | RST 6.5 is masked or disabled.        |

|      |                  | D <sub>2</sub>                                                                                  | M7.5                                                                                                              | 0                 | RST 7.5 is enabled.                   |

|      |                  | D <sub>3</sub>                                                                                  | MSE                                                                                                               | 1                 | It enables the function of            |

|      |                  | 23                                                                                              |                                                                                                                   | _                 | bits $D_2, D_1, D_0$ . This is master |

|      |                  |                                                                                                 |                                                                                                                   |                   | control over the entire               |

|      |                  |                                                                                                 |                                                                                                                   |                   | interrupt-masking bit.                |

|      |                  | D <sub>4</sub>                                                                                  | R7.5                                                                                                              | 1                 | RST 7.5 flip-flop is reset.           |

|      |                  | D <sub>5</sub>                                                                                  | x                                                                                                                 | 0                 | Undefined.                            |

|      |                  | D <sub>6</sub>                                                                                  | SDE                                                                                                               | 0                 | Disable serial output.                |

|      |                  | D <sub>7</sub>                                                                                  | SOD                                                                                                               | 0                 | Data not latched to                   |

|      |                  | - /                                                                                             |                                                                                                                   | -                 | peripheral.                           |

|      | EI               | Enable Int                                                                                      | errupt                                                                                                            | 1                 |                                       |

|      |                  |                                                                                                 |                                                                                                                   | e fli             | p-flop is set and all interrupts      |

|      |                  | are enable                                                                                      |                                                                                                                   |                   |                                       |

|      |                  | No flags a                                                                                      |                                                                                                                   |                   |                                       |

|      | MVI $A,00_{H}$   | Initialize                                                                                      |                                                                                                                   | ulato             | or.                                   |

|      |                  |                                                                                                 | STERS                                                                                                             |                   |                                       |

|      |                  |                                                                                                 | XX F                                                                                                              |                   |                                       |

|      |                  |                                                                                                 | XX C                                                                                                              |                   |                                       |

|      |                  |                                                                                                 | XX E                                                                                                              |                   |                                       |

|      |                  | H XX                                                                                            | XX L                                                                                                              |                   |                                       |

| DISP | OUT PORTA        | ∩utrut +ba                                                                                      | 00 conf                                                                                                           | 01170             | tion through port A.                  |

| DISE | MOV D,A          |                                                                                                 |                                                                                                                   |                   | to D register.                        |

|      | MOV D,A          |                                                                                                 | STERS                                                                                                             | LEIIL             | CO D TEGISCEI.                        |

|      |                  |                                                                                                 | XX F                                                                                                              |                   |                                       |

|      |                  | _                                                                                               | XX C                                                                                                              |                   |                                       |

|      |                  | 2121                                                                                            | XX E                                                                                                              |                   |                                       |

|      |                  | H XX                                                                                            | 2121                                                                                                              |                   |                                       |

|      |                  | 212                                                                                             |                                                                                                                   |                   |                                       |

|      |                  |                                                                                                 |                                                                                                                   |                   |                                       |

|      | CALL             |                                                                                                 | sub progr                                                                                                         | am.               |                                       |

| 1    |                  | Call delay                                                                                      | Sub progr                                                                                                         |                   |                                       |

|      | DELAY            |                                                                                                 |                                                                                                                   |                   |                                       |

|      |                  | D register                                                                                      | content 0                                                                                                         |                   | moved to accumulator.                 |

|      | DELAY            | D register<br><b>REGI</b>                                                                       | content 0<br>STERS                                                                                                |                   | moved to accumulator.                 |

|      | DELAY            | D register<br>REGI<br>A 00                                                                      | content 0<br>STERS<br>XX F                                                                                        |                   | moved to accumulator.                 |

|      | DELAY            | D register<br>REGI<br>A 00<br>B XX                                                              | Content 0<br>STERS<br>XX F<br>XX C                                                                                |                   | moved to accumulator.                 |

|      | DELAY            | D register<br>REGI<br>A 00<br>B XX<br>D 00                                                      | content 0<br>STERS<br>XX F<br>XX C<br>XX C<br>XX E                                                                |                   | moved to accumulator.                 |

|      | DELAY            | D register<br>REGI<br>A 00<br>B XX                                                              | content 0<br>STERS<br>XX F<br>XX C<br>XX C<br>XX E                                                                |                   | moved to accumulator.                 |

|      | DELAY<br>MOV A,D | D register<br>REGI<br>A 00<br>B XX<br>D 00<br>H XX                                              | Content 0<br>STERS<br>XX F<br>XX C<br>XX E<br>XX E<br>XX L                                                        | O <sub>H</sub> is |                                       |

|      | DELAY            | D register<br>REGI<br>A 00<br>B XX<br>D 00<br>H XX<br>Increment                                 | content 0<br>STERS<br>XX F<br>XX C<br>XX E<br>XX L<br>the accumu                                                  | O <sub>H</sub> is |                                       |

|      | DELAY<br>MOV A,D | D register<br>REGI<br>A 00<br>B XX<br>D 00<br>H XX<br>Increment<br>REGI                         | content 0<br>STERS<br>XX F<br>XX C<br>XX E<br>XX L<br>the accumu<br>STERS                                         | O <sub>H</sub> is |                                       |

|      | DELAY<br>MOV A,D | D register<br>REGI<br>A 00<br>B XX<br>D 00<br>H XX<br>Increment<br>REGI<br>A 01                 | content 0<br>STERS<br>XX F<br>XX C<br>XX E<br>XX L<br>the accumu<br>STERS<br>XX F                                 | O <sub>H</sub> is |                                       |

|      | DELAY<br>MOV A,D | D register<br>REGI<br>A 00<br>B XX<br>D 00<br>H XX<br>Increment<br>REGI<br>A 01<br>B XX         | content 0<br>STERS<br>XX F<br>XX C<br>XX E<br>XX L<br>XX L<br>the accumu<br>STERS<br>XX F<br>XX C                 | O <sub>H</sub> is |                                       |

|      | DELAY<br>MOV A,D | D register<br>REGI<br>A 00<br>B XX<br>D 00<br>H XX<br>Increment<br>REGI<br>A 01<br>B XX<br>D 00 | Content 0<br>STERS<br>XX F<br>XX C<br>XX E<br>XX L<br>the accumu<br>STERS<br>XX F<br>XX C<br>XX C<br>XX C<br>XX C | O <sub>H</sub> is |                                       |

|      | DELAY<br>MOV A,D | D register<br>REGI<br>A 00<br>B XX<br>D 00<br>H XX<br>Increment<br>REGI<br>A 01<br>B XX<br>D 00 | Content 0<br>STERS<br>XX F<br>XX C<br>XX E<br>XX L<br>the accumu<br>STERS<br>XX F<br>XX C<br>XX C<br>XX C<br>XX C | O <sub>H</sub> is |                                       |

|      | DELAY<br>MOV A,D | D register<br>REGI<br>A 00<br>B XX<br>D 00<br>H XX<br>Increment<br>REGI<br>A 01<br>B XX<br>D 00 | content 0<br>STERS<br>XX F<br>XX C<br>XX E<br>XX L<br>the accumu<br>STERS<br>XX F<br>XX C<br>XX C<br>XX E<br>XX L | O <sub>H</sub> is |                                       |

| DELAY | LXI           | Initial | ize  | the   | memory pointer at $FFFF_{H}$ .i.e. loads the 16 | - |

|-------|---------------|---------|------|-------|-------------------------------------------------|---|

|       | $B, FFFF_{H}$ | bit dat | a in | h the | e register pair designated.                     |   |

|       |               | R       | EGIS | TERS  | S                                               |   |

|       |               | A       | 00   | XX    | F                                               |   |

|       |               | В       | FF   | FF    | ] C                                             |   |

|       |               | D       | 00   | XX    | E                                               |   |

|       |               | Н       | XX   | XX    | ] L                                             |   |

| Rev. | 1.0 |

|------|-----|

|      |     |

|       |       | ${\tt C900}_{\tt H}$ is the memory pointer to the starting address of the |  |  |  |  |  |

|-------|-------|---------------------------------------------------------------------------|--|--|--|--|--|

|       |       | sine waveform look up table data sequence.                                |  |  |  |  |  |

|       |       | MEMORY                                                                    |  |  |  |  |  |

|       |       | FFFF XX                                                                   |  |  |  |  |  |

|       |       | FFFE XX<br>FFFD XX                                                        |  |  |  |  |  |

|       |       |                                                                           |  |  |  |  |  |

|       |       | FFFB XX                                                                   |  |  |  |  |  |

|       |       | XX                                                                        |  |  |  |  |  |

| AGAIN | DCX B | Decrement the BC register pair.                                           |  |  |  |  |  |

|       |       | REGISTERS                                                                 |  |  |  |  |  |

|       |       | A 00 XX F<br>B FF FE C                                                    |  |  |  |  |  |

|       |       | B FF FE C<br>D 00 XX E                                                    |  |  |  |  |  |

|       |       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                     |  |  |  |  |  |

|       |       |                                                                           |  |  |  |  |  |

|       | MOV   | The C register content is moved to accumulator.                           |  |  |  |  |  |

|       | A,C   | REGISTERS                                                                 |  |  |  |  |  |

|       |       | A FE XX F                                                                 |  |  |  |  |  |

|       |       | B FF FE C<br>D VV VV E                                                    |  |  |  |  |  |

|       |       |                                                                           |  |  |  |  |  |

|       |       | H XX XX L                                                                 |  |  |  |  |  |

|       | ORA B | OR the accumulator content with B register.                               |  |  |  |  |  |

|       |       |                                                                           |  |  |  |  |  |

|       |       | $FE_{H} => 1111 1110$                                                     |  |  |  |  |  |

|       |       | FF <sub>H</sub> => 1111 1111                                              |  |  |  |  |  |

|       |       | 1111 1111 => FF <sub>H</sub>                                              |  |  |  |  |  |

|       |       |                                                                           |  |  |  |  |  |

|       | JNZ   | Until 00 loop                                                             |  |  |  |  |  |

|       | AGAIN | -                                                                         |  |  |  |  |  |

|       | RET   | Return to main program.                                                   |  |  |  |  |  |

| ISS | PUSH PSW              | Consider that interrupt service is being called at 09                                                           |  |  |  |  |  |

|-----|-----------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|     |                       | of the accumulator during the main program execution                                                            |  |  |  |  |  |

|     | DI                    |                                                                                                                 |  |  |  |  |  |

|     | DI                    | The interrupt enable flip-flop is reset and all the                                                             |  |  |  |  |  |

|     |                       | interrupt except the TRAP are disabled.                                                                         |  |  |  |  |  |

|     |                       | No flags are affected.                                                                                          |  |  |  |  |  |

|     |                       | Comment:                                                                                                        |  |  |  |  |  |

|     |                       | This instruction is commonly used when the                                                                      |  |  |  |  |  |

|     |                       | execution of a code sequence cannot be interrupted. For                                                         |  |  |  |  |  |

|     |                       | e.g., in critical time delays, the instruction is used                                                          |  |  |  |  |  |

|     |                       | at the beginning of the code & the interrupts are                                                               |  |  |  |  |  |

|     |                       | enabled at the end of the code. The 8085 TRAP cannot be                                                         |  |  |  |  |  |

|     |                       | disabled.                                                                                                       |  |  |  |  |  |

|     |                       | disabled.                                                                                                       |  |  |  |  |  |

|     | NOT - 00              | The second se |  |  |  |  |  |

|     | MVI E,06 <sub>H</sub> | E register is initialized.                                                                                      |  |  |  |  |  |

|     |                       | REGISTERS                                                                                                       |  |  |  |  |  |

|     |                       | A 00 XX F                                                                                                       |  |  |  |  |  |

|     |                       | B XX XX C                                                                                                       |  |  |  |  |  |

|     |                       | D XX 06 E                                                                                                       |  |  |  |  |  |

|     |                       | H $XX XX$ L                                                                                                     |  |  |  |  |  |

|     |                       |                                                                                                                 |  |  |  |  |  |

|     | XRA A                 | The content of the operand are exclusive ORed with the                                                          |  |  |  |  |  |

|     |                       | content of the accumulator, and the results are placed                                                          |  |  |  |  |  |

|      |                  | in the accumulator. The content of the operand is not                         |

|------|------------------|-------------------------------------------------------------------------------|

|      |                  | altered.<br>Flags: Z,S,P are altered. CY,AC are reset.                        |

|      |                  | riago. Aforr are arcerea. erfne are rebet.                                    |

|      |                  | REGISTERS                                                                     |

|      |                  | A         00         XX         F           B         XX         XX         C |

|      |                  | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                         |

|      |                  | H XX XX L                                                                     |

|      |                  | XRA A instruction is used for clearing the accumulator                        |

|      |                  | to 00 thereby initializing register A.                                        |

| NEXT | CMA              | The accumulator content is complemented, no flags are                         |

|      |                  | affected.<br>REGISTERS                                                        |

|      |                  | A FF XX F                                                                     |

|      |                  | B XX XX C                                                                     |

|      |                  | D XX XX E                                                                     |

|      |                  | H XX XX L                                                                     |

|      | OUT PORTA        |                                                                               |

|      | MOV M,A          | The accumulator content is moved to memory.<br>REGISTERS                      |

|      |                  | A FF XX F                                                                     |

|      |                  | B XX XX C                                                                     |

|      |                  | D XX 06 E                                                                     |

|      |                  | H XX XX L                                                                     |

|      | CALL             | Make the glowing visible by considerable time delay.                          |

|      | DELAY<br>MOV A,M | The memory content is moved to accumulator.                                   |

|      | MOV A,M          | REGISTERS                                                                     |

|      |                  | A FF XX F                                                                     |

|      |                  | B XX XX C                                                                     |

|      |                  | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                        |

|      |                  |                                                                               |

|      | DCR E            | The E register content is decremented.                                        |

|      |                  | REGISTERS<br>A FE XX F                                                        |

|      |                  | B XX XX C                                                                     |

|      |                  | D XX 05 E                                                                     |

|      |                  | H XX XX L                                                                     |

|      | JNZ NEXT         | Until 00 the loop continues                                                   |

|      |                  | The LED glows FF & OO alternatively.                                          |

|      |                  | When E=06 => FF GLOW                                                          |

|      |                  | When $E=05 \implies 00 \text{ GLOW}$                                          |

|      |                  | When $E=04 \implies FF$ GLOW                                                  |

|      |                  | When $E=03 \implies 00$ GLOW<br>When $E=02 \implies$ FF GLOW                  |

|      |                  | When $E=01 \implies 00$ GLOW                                                  |

|      |                  | Thus during ICC the IEDs alors alternatively show                             |

|      |                  | Thus during ISS, the LEDs glow alternatively when interrupted.                |

|      |                  | Since now the interrupt has been disabled in order to                         |

|      |                  | perform this blinking action.                                                 |

| EI      | Enable interrupt                                                                                                                                             |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POP PSW | Now, note that the accumulator is restored with the value 09 , where the interrupt service was called. Hence the main program continues with the next count. |

| RET     | Return to main program, where vector interrupt was being pressed.                                                                                            |

#### VERIFICATION

During the execution of the program, while the LED's start counting, press the vector interrupt button. Then it goes to ISS that is blinking display. It blinks few times and then starts counting from the previous count.

#### OBSERVATION

```

Hardware interrupt = RST 7.5

Vector location = 003C<sub>H</sub>

```

```

In ROM at (003C )=C3<sub>H</sub>

(003D )=B1<sub>H</sub>

(003E )=FF<sub>H</sub>

=>JMP FFB1<sub>H</sub>

```

```

In user RAM at (FFB1 )=C3 <sub>H</sub>

(FFB2 )=00 <sub>H</sub>

(FFB3 )=C5 <sub>H</sub>

=>JMP C500 <sub>H</sub>

In general, JMP "ISS LOCATION"

```

## REFERENCE

- 1. Ramesh S.Gaonkar, Microprocessor Architecture, Programming, and Applications, Fourth Edition, Penram International Publishing (India), 2000.

- 2. S.Subathra, "Advanced Microprocessor Laboratory", Record work, Adhiparashakthi Engineering College, Melmaruvathur, October 2002

- S.Subathra, "Programming in 8085 Microprocessor and its applications An Innovative Analysis", Technical Report, Adhiparashakthi Engineering College, Melmaruvathur, March 2003

- 4. Micro-85 EB, User Manual, Version 3.0, CAT #M85 EB-002, VI Microsystems Pvt. Ltd., Chennai.