# COMMUNICATION BETWEEN TWO MICROPROCESSOR

# BY SUBATHRA S

This work is licensed under the Creative Commons Attribution-NonCommercial-Share Alike 2.5 India License. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-sa/2.5/in/deed.en or send a letter to Creative Commons, 171 Second Street, Suite 300, San Francisco, California, 94105, USA.

# COMMUNICATION BETWEEN TWO MICROPROCESSORS

#### OBJECTIVE

To establish communication between the two 8085 Microprocessor by writing an assembly language program to transmitter and receiver

#### **APPARATUS REQUIRED**

- Single board microcomputer (VI Microsystems 85).

- RS 232 Connector.

- Flat Ribbon Cable.

#### DESCRIPTION

When data are transmitted as voltage, the commonly used standard is known as RS – 232C. It is defined in reference to data terminal equipment (DTE) and data communication equipment (DCE) terminal and modern. Its voltage levels are not compatible with TTL logic levels. The rate of data transmission in RS – 232C, is restricted to a maximum of 20k baud and a distance of 50ft, for high speed data transmission, new standards RS - 422A and RS - 423A developed in recent years.

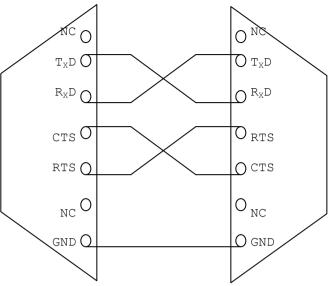

The RS – 232C is a 25 pin connector and its signals are divided in to four groups signals, control signals, timing signals and ground.

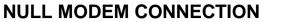

The minimum interface between a computer and a peripheral requires three lines 2, 3, and 7. These lines are defined in relation to the DTE, the terminal transmits on pin2, and receiver other hand, the DCE transmits on pin3, receiver on pin2. The transmit and receive lines cross, hence it is known as NULL – MODEM CONNECTION.

## ALGORITHM

Transmitter

- Initialize the timer and USART of the transmitter.

- Set the starting address of data to be transmitted and the number of bytes to be transmitted.

- Program the USART for serial data transmission.

- Stop the execution.

#### Receiver

- Intialize the timer and USART of receiving data.

- Set the starting address of data received.

- Program the USART for serial data reception.

- Receive the data from RS-232 pin and stop the execution.

#### RS 232 DETAILS - 25 PIN

| PIN  | SIGNALS                                         |

|------|-------------------------------------------------|

| 1    | Protective ground                               |

| 2    | Transmitted data (TXD) -> DCE                   |

| 3    | Received data (RXD) -> DTE                      |

| 4    | Request to send (RST)->DCE                      |

| 5    | Clear to send (CTS) -> DTE                      |

| 6    | Data set ready (DSR) -> DTE                     |

| 7    | Signal ground                                   |

| 8    | Received line signal detector                   |

| 9,10 | Reserved for data set testing                   |

| 11   | Unassigned                                      |

| 12   | Secondary Clear to send                         |

| 13   | Secondary Recorded line signal detector         |

| 14   | Secondary Transmitted data                      |

| 15   | Transmission signal element timing (DCE source) |

| 16   | Secondary Received data                         |

| 17   | Receiver signal element timing (DCE source)     |

| 18   | Unassigned                                      |

| 19   | Secondary request to send                       |

| 20   | DCE <- data terminal ready (DTR)                |

| 21   | Signal quality detector                         |

| 22   | ring indicator                                  |

| 23 | data signal rate selector (DTE/DCE source) |

|----|--------------------------------------------|

| 24 | Transmit signal element timing             |

| 25 | Unassigned                                 |

# **COMMAND INSTRUCTION FORMAT OF 8251A**

| DATA BIT DESCRIPTION  |      | DESCRIPTION                                                    |  |  |  |                 |  |  |  |  |  |

|-----------------------|------|----------------------------------------------------------------|--|--|--|-----------------|--|--|--|--|--|

| D <sub>0</sub>        | TXEN | TRANSMIT ENABLE                                                |  |  |  | TRANSMIT ENABLE |  |  |  |  |  |

|                       |      | 1 - ENABLE ; 0 - DISABLE                                       |  |  |  |                 |  |  |  |  |  |

| $D_1$                 | DTR  | DATA TERMINAL READY                                            |  |  |  |                 |  |  |  |  |  |

|                       |      | 'HIGH' WILL FORCE DTR OUTPUT TO 0                              |  |  |  |                 |  |  |  |  |  |

| <b>D</b> <sub>2</sub> | RXE  | RECEIVE ENABLE                                                 |  |  |  |                 |  |  |  |  |  |

|                       |      | 1 - ENABLE ; 0 - DISABLE                                       |  |  |  |                 |  |  |  |  |  |

| <b>D</b> <sub>3</sub> | SBRK | SEND BREAK CHARACTER                                           |  |  |  |                 |  |  |  |  |  |

|                       |      | 1 = FORCE TXD "LOW"                                            |  |  |  |                 |  |  |  |  |  |

|                       |      | 0 = NORMAL OPERATION                                           |  |  |  |                 |  |  |  |  |  |

| $D_4$                 | ER   | ERROR RESET                                                    |  |  |  |                 |  |  |  |  |  |

|                       |      | 1 = RESET ERROR FLAGS OF, PE, OE, FE                           |  |  |  |                 |  |  |  |  |  |

| <b>D</b> <sub>5</sub> | RTS  | REQUEST TO SEND "HIGH " WILL FORCE RTS OUPUT TO 0              |  |  |  |                 |  |  |  |  |  |

| <b>D</b> <sub>6</sub> | IR   | INTERNAL RESET "HIGH" RETURNS 8251A TO MODE INSTRUCTION FORMAT |  |  |  |                 |  |  |  |  |  |

| <b>D</b> <sub>7</sub> | EH   | ENTER HUNT MODE                                                |  |  |  |                 |  |  |  |  |  |

|                       |      | 1 - ENABLE A SEARCH FOR SYNCRONOUS CHARACTER                   |  |  |  |                 |  |  |  |  |  |

|                       |      | ( HAS NO EFFECT IN ASYNCRONOUS MODE )                          |  |  |  |                 |  |  |  |  |  |

# **STATUS WORD FORMAT 8251A**

| DA                    | TA BIT  | DESCRIPTION                                                                                                                                                                                                                                                                 |

|-----------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>0</sub>        | TXRDY   | TRANSMITTER READY<br>TXRDY status bit has different meanings from the TXRDY output pin. The former is not<br>conditioned by CTS & TXEN (i.e) TXRDY status bit = DB buffer empty TXRDY pin out =                                                                             |

|                       |         | DB buffer empty. (CTS – 0) (TXEN – 1).                                                                                                                                                                                                                                      |

| D1                    | RXRDY   | RECEIVER READY<br>This bit indicates that the 8251A contains a character that is ready to be input to the CPU                                                                                                                                                               |

| $D_2$                 | TXEMPTY | TRANSMITTER EMPTY                                                                                                                                                                                                                                                           |

|                       |         | When the 8251A has no character to transmit this bit will go high                                                                                                                                                                                                           |

| D3                    | PE      | PARITY ERROR<br>The PE flag is set when a parity error is detected. It is reset by the ER bit of the command<br>instruction. PE does not inhibit operation of the 8251A                                                                                                     |

| D <sub>4</sub>        | OE      | OVERFLOW ERROR<br>The OE flag is set when the CPU does not read a character before the next one becomes<br>available. OE is reset by the ER bit of the command instruction. OE does not inhibit the<br>operation of 8251A however the previously overrun character is lost. |

| D <sub>5</sub>        | FE      | FRAMING ERROR(Asynchronous mode only)<br>The FE flag is set when a valid stop bit is not detected at end of every character. It is reset<br>by the ER BIT of the command instruction. FE does not inhibit the operation of 8251A.                                           |

| D <sub>6</sub>        | SYNDET  | SYNC DETECT<br>This pin is used in synchronous mode for syndet and is used in asynchronous mode for<br>break detect.                                                                                                                                                        |

| <b>D</b> <sub>7</sub> | DSR     | DATA SET READY<br>Indicates that the DSR is at zero level.                                                                                                                                                                                                                  |

| DATA                  |     | DESCRIPTION                  |      |           |          |  |

|-----------------------|-----|------------------------------|------|-----------|----------|--|

|                       |     | DESCRIPTION                  |      |           |          |  |

| BI                    | -   |                              |      |           |          |  |

| $\mathbf{D}_0$        | в1  | Baud                         | rat  | e Factor  |          |  |

|                       |     | В2                           | В1   |           |          |  |

|                       |     | 0                            | 0    | Syncrono  | ous mode |  |

| $D_1$                 | в2  | 0                            | 1    | 1X        |          |  |

|                       |     | 1                            | 0    | 16X       |          |  |

|                       |     | 1                            | 1    | 64X       |          |  |

| $D_2$                 | L1  | Char                         | acte | er Length |          |  |

|                       |     | L2                           | L1   |           |          |  |

|                       |     | 0                            | 0    | 5 bits    |          |  |

| $D_3$                 | L2  | 0 1 6 bits                   |      |           |          |  |

|                       |     | 1                            | 0    | 7 bits    |          |  |

|                       |     | 1                            | 1    | 8 bits    |          |  |

| $D_4$                 | PEN | Parity Enable                |      |           |          |  |

|                       |     | 1 - ENABLE                   |      |           |          |  |

|                       |     | 0 - DISABLE                  |      |           |          |  |

| $D_5$                 | EP  | Even parity Generation Check |      |           |          |  |

|                       |     | 0 -                          | ODD  |           |          |  |

|                       |     | 1 - EVEN                     |      |           |          |  |

| $D_6$                 | S1  | No of Stop bit               |      |           |          |  |

|                       |     | S2                           | S1   |           |          |  |

|                       |     | 0                            | 0    | Invalid   |          |  |

| <b>D</b> <sub>7</sub> | S2  | 0                            | 1    | 1 bit     |          |  |

|                       |     | 1                            | 0    | 1.5 bits  | 3        |  |

|                       |     | 1                            | 1    | 2 bits    |          |  |

# **CONTORL WORD FORMAT 8253**

| DA'            | TA BIT | DESCRIPTION    |            |   |    |        |  |

|----------------|--------|----------------|------------|---|----|--------|--|

| D <sub>0</sub> | BCD    | BINA           | BINARY/BCD |   |    |        |  |

| $D_1$          | M0     | MODE           |            |   |    |        |  |

|                |        | M2             | M1         | ľ | 40 | MODE   |  |

| $D_2$          | M1     | 0              | 0          | ( | )  | 0      |  |

|                |        | 0              | 0          | - | L  | 1      |  |

|                |        | 0              | 1          | ( | )  | 2<br>3 |  |

| $D_3$          | M2     | 0              | 1          | - | L  | 3      |  |

|                |        | 1              | 0          | ( | )  | 4      |  |

|                |        | 1              | 0          | 1 | L  | 5      |  |

| $D_4$          | RL0    | READ           | /LOA       | D |    |        |  |

|                |        | RL1            | RL(        | ) |    |        |  |

|                |        | 0              | 0          |   | Lá | atch   |  |

| $D_5$          | RL1    | 0              | 1          |   | ΓS | SB     |  |

|                |        | 1              | 0          |   | MS | SB     |  |

|                |        | 1              | 1          |   | LS | SB/MSB |  |

| $D_6$          | SC0    | SELECT COUNTER |            |   |    |        |  |

|                |        | SC0            | SC         | 1 | CF | 1#     |  |

|                |        | 0              | 0          |   | 0  |        |  |

| $D_7$          | SC1    | 0              | 1          |   | 1  |        |  |

|                |        | 1              | 0          |   | 2  |        |  |

|                |        | 1              | 1          |   | Х  |        |  |

## ASSEMBLY LANGUAGE PROGRAM

| Transmitter |       |                         |                |                                                                               |

|-------------|-------|-------------------------|----------------|-------------------------------------------------------------------------------|

| ADDRESS     | LABEL | MNEMONICS               | OPCODE/OPERAND | COMMENT                                                                       |

| 4100        |       | MVI A,36 <sub>H</sub>   | 3E 36          | Initialization of 8253                                                        |

| 4102        |       | OUT TMRCNT              | D3 0B          |                                                                               |

| 4104        |       | MVI A,0A <sub>H</sub>   | 3E 0A          |                                                                               |

| 4106        |       | OUT TMRCHO              | D3 08          |                                                                               |

| 4108        |       | XRA A                   | AF             |                                                                               |

| 4109        |       | OUT TMRCHO              | D3 08          |                                                                               |

| 410B        |       | XRA A                   | AF             | Resetting the                                                                 |

| 410C        |       | OUT UATCNT              | D3 05          | 8251A                                                                         |

| 410E        |       | MVI A,40 <sub>H</sub>   | 3E 40          |                                                                               |

| 4110        |       | OUT UATCNT              | D3 05          |                                                                               |

| 4112        |       | MVI A,4E <sub>H</sub>   | 3E 4E          | Initialization of                                                             |

| 4114        |       | OUT UATCNT              | D3 05          | 8251A                                                                         |

| 4116        |       | MVI A,37 <sub>H</sub>   | 3E 37          |                                                                               |

| 4118        |       | OUT UATCNT              | D3 05          |                                                                               |

| 411A        |       | LXI H,4300 <sub>H</sub> | 21 00 43       | Load the input data                                                           |

|             |       | , II                    |                | in to transmitter memory                                                      |

| 411D        |       | MVI C,05 <sub>н</sub>   | 0E 05          | Initialize the<br>number of input<br>data count                               |

| 411F        | LOOP  | IN UATCNT               | DB 05          | Check 8251A                                                                   |

| 4121        |       | ANI 04 <sub>H</sub>     | E6 04          | TXEMPTY and                                                                   |

| 4123        |       | JZ LOOP                 | CA 1F 41       | then send the data                                                            |

| 4126        |       | MOV A,M                 | 7E             | Move the recent<br>input data to<br>accumulator                               |

| 4127        |       | INX H                   | 23             | Increment the<br>memory location to<br>get the next data in<br>to transmitter |

| 4128        |       | OUT UATDAT              | D3 04          | Transmit the data to receiver                                                 |

| 412A        |       | DCR C                   | 0D             | Decrement the<br>input data count                                             |

| 412B        |       | JNZ LOOP                | C2 1F 41       | Until all data are<br>transmitted<br>continue looping                         |

| 412E        |       | HLT                     | 76             | Stop the execution                                                            |

| Receiver    |       |                         |                |                                                                               |

| 4200        |       | MVI А,36 н              | 3E 36          | Initialisation of 8253                                                        |

| 4202        |       |                         | D3 0B          |                                                                               |

| 4204        |       | MVI A,0A <sub>H</sub>   | 3E 0A          | 1                                                                             |

| 4206        |       |                         | D3 08          | 1                                                                             |

| 4208        |       | XRA A                   | AF             | 1                                                                             |

| 420A        |       | OUT TMRCHO              | D3 08          | 1                                                                             |

| 420R        |       | XRA A                   | AF             | Resetting the                                                                 |

| 420B        |       |                         | D3 05          | 8251A                                                                         |

| 420C        |       | MVI A,40 <sub>H</sub>   | 3E 40          |                                                                               |

| 420E        |       |                         | D3 05          | 4                                                                             |

| 4210        |       | MVI A,4E <sub>H</sub>   | 3E 4E          | Initialization of                                                             |

|             |       |                         |                |                                                                               |

| 4214        |       | OUT UATCNT              | D3 05          | 8251A                                                                         |

| 4216 |       | MVI A,37 <sub>H</sub>   | 3E 37    |                     |

|------|-------|-------------------------|----------|---------------------|

| 4218 |       | OUT UATCNT              | D3 05    |                     |

| 421A |       | LXI H,4400 <sub>H</sub> | 21 00 44 | Load the output     |

|      |       |                         |          | data in to receiver |

|      |       |                         |          | memory              |

| 421D |       | MVI C,05 <sub>H</sub>   | 0E 05    | Initialize the      |

|      |       | ,                       |          | number of input     |

|      |       |                         |          | data count          |

| 421F | LOOP1 | IN UATCNT               | DB 05    | Check 8251A         |

| 4221 |       | ANI 02 <sub>H</sub>     | E6 02    | RXEMPTY and         |

| 4223 |       | JZ LOOP1                | CA 1F 42 | hence get the data  |

|      |       |                         |          | and store the data  |

| 4226 |       | IN UATDAT H             | DB 04    | Receive the data    |

|      |       |                         |          | from transmitter    |

| 4228 |       | MOV M,A                 | 77       | Move the recent     |

|      |       |                         |          | input data to       |

|      |       |                         |          | accumulator         |

| 4229 |       | DCR C                   | 0D       | Decrement the       |

|      |       |                         |          | receiver data count |

| 422A |       | INX H                   | 23       | Increment the       |

|      |       |                         |          | memory location to  |

|      |       |                         |          | store the           |

|      |       |                         |          | transmitted data    |

| 422B |       | JNZ LOOP                | C2 1F 42 | Until all data are  |

|      |       |                         |          | received continue   |

|      |       |                         |          | looping             |

| 422E |       | HLT                     | 76       | Stop the execution  |

#### **EXECUTION**

#### Transmitter

| Tunshintor        |                        |  |  |  |  |

|-------------------|------------------------|--|--|--|--|

| ADDRESS           | DATA                   |  |  |  |  |

| 4300 <sub>H</sub> | $AA_{H}$               |  |  |  |  |

| 4301 <sub>H</sub> | $BB_{{}_{\mathrm{H}}}$ |  |  |  |  |

| 4302 <sub>H</sub> | CCH                    |  |  |  |  |

| 4303 <sub>H</sub> | $DD_{\mathrm{H}}$      |  |  |  |  |

| 4304 <sub>H</sub> | EE                     |  |  |  |  |

|                   |                        |  |  |  |  |

# Receiver

| ADDRESS           | DATA              |

|-------------------|-------------------|

| 4400 <sub>H</sub> | $AA_{H}$          |

| 4401 <sub>H</sub> | $BB_{\mathbb{H}}$ |

| 4402 <sub>H</sub> | CC <sub>H</sub>   |

| 4403 <sub>H</sub> | $DD_{\mathrm{H}}$ |

| 4404 <sub>H</sub> | EE                |

|                   |                   |

# REFERENCE

1. Ramesh S.Gaonkar, Microprocessor Architecture, Programming, and Applications, Fourth Edition, Penram International Publishing (India), 2000.

- 2. S.Subathra, "Advanced Microprocessor Laboratory", Record work, Adhiparashakthi Engineering College, Melmaruvathur, October 2002

- 3. S.Subathra, "Programming in 8085 Microprocessor and its applications An Innovative Analysis", Technical Report, Adhiparashakthi Engineering College, Melmaruvathur, March 2003

- 4. Micro-85 EB, User Manual, Version 3.0, CAT #M85 EB-002, VI Microsystems Pvt. Ltd., Chennai.